韦豪创芯:键合设备-先进封装领域关键设备(上)

【编者按】本文由韦豪创芯 张迪 供稿,集微网经授权转发。

随着先进封装在算力时代的重要性日益凸显,键合设备成为不可或缺的关键设备。作为韦豪创芯本期月度思考的重要着眼点,本报告力图对键合设备的发展情况进行梳理,为相关投资提供有益的参考意见。

一、晶圆键合

晶圆键合(Bonding)是将两个或多个晶圆通过物理或化学方法紧密结合在一起的工艺。用以实现芯片连接、减小封装尺寸、或者提高晶圆结构强度,避免晶圆在后续加工中变形等各种用途。

后摩尔时代下,通过芯片制程线宽的缩小提升芯片性能的方式越来越困难,芯片设计端和生产制造端转而通过将器件结构从平面MOSFET改为FinFET/GAA等 “鳍” 状立体结构增加了栅极与沟道的接触面积,提升对迁移电子的控制能力及减少漏电现象。在封装集成方面进行Chiplet异构集成封装、CoWoS、HBM等2.5D/3D封装形式提升互联带宽和集成密度,增强性能的同时能够取得性价比。

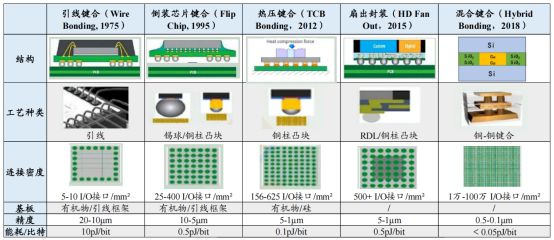

先进封装追求更高的传输速度、更小的芯片尺寸,作为先进封装的核心技术,键合工艺经历了从最初通过引线框架到倒装(FC)、热压粘合(TCP)、扇出封装(Fan-out)、混合封装(Hybrid Bonding)的演变,追求更快的互联速度。可以看到键合工艺的改进升级极大的推动了I/O接口密度的提升,也就大幅度提升了芯片的传输带宽。

封装形式发展

图片来源:BESI、东吴证券研究所

各大厂商也将先进封装视为关键技术不断推进,例如台积电推出了CoWoS、SoIC等,英特尔推出了EMIB、Foveros 和Co-EMIB等,三星也推出了FOPLP等2.5D/3D堆叠封装技术,海力士、三星、美光等积极投入的HBM存储芯片也同样是采用的3D堆叠方式。封装要求的不断提高,先进封装对键合工艺的要求也越来越高,如更高的键合强度、更好的平整度、更小的键合尺寸等。

二、不同的键合方式的应用场景

① 无图形片的键合

无图形片的键合通常会采用临时键合的方案,临时键合一般有临时热压键合和UV固化两种方式。临时键合首先要将临时键合胶通过旋涂或喷涂方式在器件晶圆和载片表面均匀涂布,随后依靠热压临时键合或UV固化临时键合方式,使载片和晶圆键合牢固。

3D堆叠层数的提高受限于堆叠后的厚度、散热、以及后续的TSV工艺的适配性,晶圆减薄工艺成为先进封装的核心工艺。在一些先进的封装应用中,需要将晶圆减薄至50μm以下,晶圆减薄工艺需要引入临时键合、解键合以提供机械支撑。同时也有部分做碳化硅芯片的晶圆厂,考虑到碳化硅的易碎性,在进行研磨或减薄工艺之前,会通过临时键合叠加一片同尺寸的硅片/玻璃圆片,之后进行研磨工艺,可以大幅降低碎片的风险,之后再进行解键合。

② 有图形片键合/IC芯片的键合

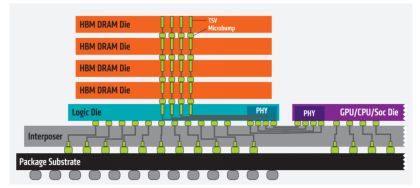

1)高带宽存储器(HBM),垂直堆叠多个DRAM,通过TSV铜连接,可显著提升传输带宽。HBM早期主要采用TC-NCF热压键合工艺,随着堆叠层数的增加,对散热要求越来越高,SK海力士在最新的HBM3E中率先使用改进的MR-MUF工艺,三星和美光仍以TC-NCF热压键合技术为主。在更高层数的HBM生产中各家预期将陆续引入混合键合工艺。

图片来源:AMD、华安证券研究所

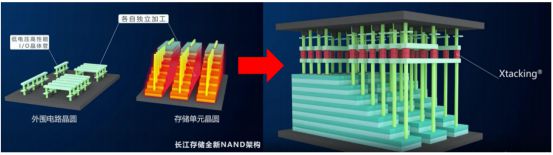

2)传统3D NAND架构中,外围电路约占芯片面积的20~30%,随着堆叠层数增加,外围电路面积占比可能超过50%,导致芯片存储密度急剧下降。而长江存储Xtacking技术通过将存储单元和外围电路分别放在两片晶圆上,然后通过垂直互联通道将二者键合。能够显著缓解多堆叠NAND的外围电路占芯片面积,提高存储密度。

图片来源:长江存储、东吴证券研究所

3)采用同样原理的还有CIS芯片,将CMOS感光单元与逻辑电路分别在不同的晶圆上制作,再将2片/3片晶圆键合连接起来,形成堆叠芯片,这种方式不仅提高了感光面积,提升图像传感器的灵敏度、分辨率等关键指标。还可以将CMOS、逻辑电路采用不同的制程工艺生产,提升效率,降低生产成本。

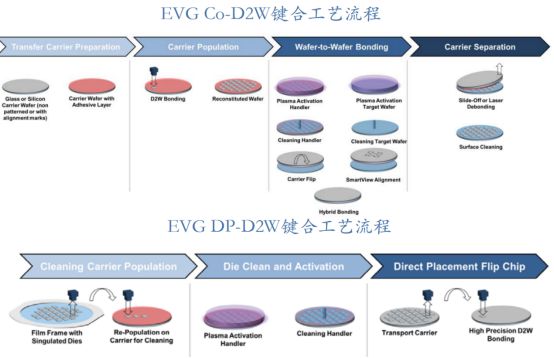

③ 按键合对象可划分为晶圆-晶圆键合(Wafer-to-Wafer,W2W)和芯片-晶圆键合(Die-to-Wafer,D2W)

图片来源:EVG、华安证券研究所

1)芯片-晶圆键合(Die-to-Wafer,D2W)

C2W 键合是将单个芯片与整个晶圆进行键合。通常先在芯片和晶圆的表面制备相应的键合层,然后通过施加一定的压力、温度和化学作用等,使芯片与晶圆上对应的位置实现连接。

C2W 键合的灵活性高,可以根据具体需求选择不同类型、不同功能的芯片与晶圆进行键合,适用于小批量、多品种的生产需求,能够快速实现产品的定制化。同时由于是单个芯片与晶圆键合,即使某个芯片存在缺陷,也不会影响其他芯片的键合,只需更换有问题的芯片即可,提高了生产的良率和效率。

但要将单个芯片准确地键合到晶圆上的指定位置,需要高精度的对准技术,否则可能导致芯片与晶圆之间的电气连接不良或机械结合不牢固。另一方面,逐个芯片进行键合,操作步骤较多,相比W2W 键合方式,生产效率较低,因此在大规模生产时成本相对较高。

2)晶圆-晶圆键合(Wafer-to-Wafer,W2W)

W2W 键合是将两片晶圆直接进行键合。首先对两片晶圆的表面进行处理,使其具有良好的亲水性或形成特定的键合层,然后将两片晶圆精确对准并贴合在一起,在一定的工艺条件下实现晶圆之间的大面积键合。

W2W 键合的生产效率高,一次键合可以完成整个晶圆面的连接,相比C2W 键合方式,大大减少了键合的次数和时间,适用于大规模生产,能够有效降低生产成本。同时对准精度相对容易控制,由于是两片晶圆整体进行对准,相对于C2W 键合中单个芯片的对准,更容易实现较高的对准精度,且键合后的一致性较好。

另一方面,灵活性不如C2W 键合,更适合同类芯片进行堆叠,如HBM芯片。缺陷影响范围大,如果其中一片晶圆存在缺陷,那么在键合后整个晶圆的质量都会受到影响,导致整片晶圆报废的风险较高,W2W 键合对晶圆的制造工艺和质量控制要求更为严格。

【未完待续】